### РОСЖЕЛДОР

# **Федеральное государственное бюджетное образовательное учреждение** высшего образования

# Ростовский государственный университет путей сообщения (ФГБОУ ВО РГУПС)

Лиховской техникум железнодорожного транспорта (ЛиТЖТ – филиал РГУПС)

#### ДОКУМЕНТ ПОДПИСАН ЭЛЕКТРОННОЙ ПОДПИСЬЮ

Сертификат 41085aad477861a681676be74f996ebe Владелец Полухина Виктория Ивановна Действителен с 20.04.2023 до 13.07.2024

# ФОНД ОЦЕНОЧНЫХ СРЕДСТВ

# по дисциплине ОП.08. ЦИФРОВАЯ СХЕМОТЕХНИКА

для специальности:

27.02.03 Автоматика и телемеханика на транспорте (железнодорожном транспорте)

г. Каменск-Шахтинский

### Рассмотрено

на заседании ЦМК ОПД и ПМ специальности 27.02.03 протокол от 19.06.2023 №1

Председатель ЦМК

Л.В. Пешина

Утверждаю:

Заместитель директора по УР

В.И. Полухина

19.06.202

**Автор-составитель** Пешина Л.В., преподаватель высшей квалификационной категории.

# Содержание

| 1. Паспорт фонда оценочных средств                                  |   |  |  |  |  |

|---------------------------------------------------------------------|---|--|--|--|--|

| 2. Результаты освоения учебной дисциплины, подлежащие проверке      | 4 |  |  |  |  |

| 3. Оценка освоения учебной дисциплины                               | 6 |  |  |  |  |

| 3.1. Описание системы оценивания                                    | 6 |  |  |  |  |

| 3.2. Перечень оценочных средств                                     |   |  |  |  |  |

| 3.3 Формы и методы оценивания                                       |   |  |  |  |  |

| 4 Задания для оценки освоения учебной дисциплины                    |   |  |  |  |  |

| 4.1. Задания для текущего контроля                                  |   |  |  |  |  |

| 4.2. Задания для проведения рубежного контроля                      |   |  |  |  |  |

| 4.3. Фонд оценочных средств для проведения промежуточной аттестации |   |  |  |  |  |

| (экзамен)                                                           |   |  |  |  |  |

# 1. Паспорт фонда оценочных средств на весь срок изучения дисциплины

Фонд оценочных средств (далее – ФОС) предназначен для контроля и оценки образовательных достижений обучающихся, освоивших программу учебной дисциплины ОП.08. Цифровая схемотехника

ФОС включает контрольные материалы для проведения текущего контроля, рубежного и промежуточного контроля разработан на основе Федерального государственного образовательного стандарта среднего профессионального образования по специальности 27.02.03 «Автоматика и телемеханика на транспорте (железнодорожном транспорте) примерной программы учебной дисциплины ОП.09. Цифровая схемотехника.

В структуре основной профессиональной образовательной программы данная дисциплина относится к циклу ОПД и ПМ специальности 27.02.03.

Формой промежуточной аттестации по учебной дисциплине является экзамен.

### 2. Результаты освоения учебной дисциплины, подлежащие проверке

Контроль и оценка результатов освоения учебной дисциплины осуществляется в процессе проведения практических и лабораторных занятий, тестирования, а также выполнения обучающимися индивидуальных заданий и экзамена.

В результате освоения учебной дисциплины обучающейся должен уметь:

- У1.использовать типовые средства вычислительной техники и программного обеспечения;

- У2.проводить контроль и анализ процесса функционирования цифровых схемотехнических устройств по функциональным схемам.

#### знать:

- 31. виды информации и способы ее представления в ЭВМ;

- 32. алгоритмы функционирования цифровой схемотехники.

# В результате изучения дисциплины Цифровая схемотехника обучающиеся должны овладеть следующими компетенциями:

#### Общие компетенции

| Выбирать способы решения задач профессиональной деятельности               |

|----------------------------------------------------------------------------|

| применительно к различным контекстам;                                      |

| Использовать современные средства поиска, анализа и интерпретации          |

| информации и информационные технологии для выполнения задач                |

| профессиональной деятельности;                                             |

| Планировать и реализовывать собственное профессиональное и личностное      |

| развитие, предпринимательскую деятельность в профессиональной сфере,       |

| использовать знания по финансовой грамотности в различных жизненных        |

| ситуациях;                                                                 |

| Эффективно взаимодействовать и работать в коллективе и команде;            |

| Осуществлять устную и письменную коммуникацию на государственном языке     |

| Российской Федерации с учетом особенностей социального и культурного       |

| контекста;                                                                 |

| Проявлять гражданско-патриотическую позицию, демонстрировать осознанное    |

| поведение на основе традиционных общечеловеческих ценностей, в том числе с |

| учетом гармонизации межнациональных и межрелигиозных отношений,            |

| применять стандарты антикоррупционного поведения;                          |

| Пользоваться профессиональной документацией на государственном и           |

| иностранном языках.                                                        |

|                                                                            |

### Профессиональные компетенции

| ПК 1.1 | Анализировать работу станционных, перегонных, микропроцессорных и |

|--------|-------------------------------------------------------------------|

|        | диагностических систем автоматики по принципиальным схемам        |

### ЛР 1. Осознающий себя гражданином и защитником великой страны.

- ЛР2. Проявляющий активную гражданскую позицию, демонстрирующий приверженность принципам честности, порядочности, открытости, экономически активный и участвующий в студенческом и территориальном самоуправлении, в том числе на условиях добровольчества, продуктивно взаимодействующий и участвующий в деятельности общественных организаций;

- ЛР 3. Соблюдающий нормы правопорядка, следующий идеалам гражданского общества, обеспечения безопасности, прав и свобод граждан России. Лояльный к установкам и проявлениям представителей субкультур, отличающий их от групп с деструктивным и девиантным поведением. Демонстрирующий неприятие и предупреждающий социально опасное поведение окружающих;

- ЛР 4. Проявляющий и демонстрирующий уважение к людям труда, осознающий ценность собственного труда. Стремящийся к формированию в сетевой среде личностно и профессионального конструктивного «цифрового следа»

- ЛР 7. Осознающий приоритетную ценность личности человека; уважающий собственную и чужую уникальность в различных ситуациях, во всех формах и видах деятельности;

- ЛР 24. Ценностное отношение обучающихся к культуре, и искусству, к культуре речи и культуре поведения, к красоте и гармонии;

- ЛР 27. Осознающий единство пространства Ростовской области какединой среды обитания всех населяющих ее национальностей и народов, определяющей общность их исторических судеб; уважающий религиозные убеждения, традиции и культуру народов, проживающих на территории области;

### 3. Оценка освоения учебной дисциплины

#### 3.1. Описание системы оценивания.

Предметом оценки служат знания и умения, предусмотренные ППССЗ по дисциплине ОП.08. Цифровая схемотехника, направленные на формирование профессиональных и общих компетенций.

Текущая, рубежная и промежуточная аттестации студентов по дисциплине проводятся в соответствии с существующими нормативными документами и являются обязательными.

**Текущая аттестация** по дисциплине проводится в форме контрольных мероприятий по оцениванию фактических результатов обучения студентами дисциплины.

Объектами оценивания выступают:

- учебная дисциплина (активность на занятиях, своевременность выполнения различных видов заданий, посещаемость всех видов занятий по аттестуемой дисциплине);

- степень усвоения теоретических знаний;

- уровень овладения практическими умениями и навыками по всем видам учебной работы;

- результаты самостоятельной работы.

Текущий контроль должен обеспечивать количественную оценку знаний, умений и навыков студентов и отражаться в учебном журнале

**Рубежный контроль** — это проверка уровня усвоения очередного раздела или темы по дисциплине. Проводится в виде тестирования и выполнения 2-х контрольных работ.

Задания должны быть адекватны этапу познавательной деятельности обучаемых, каждому элементу структуры которой может соответствовать серия из нескольких заданий. Рубежный контроль может служить в качестве своеобразного входного контроля для допуска к изучению последующего материала и поддержки уровня знаний при больших перерывах в работе.

**Промежуточная аттестация в форме экзамена** проводится после сдачи всех заданий текущей и рубежной аттестации.

К экзамену допускаются студенты, не имеющие задолженности по изучаемым темам при условии выполнения всех практических и лабораторных занятий. При явке на экзамен (по окончанию изучения дисциплины) студентам необходимо иметь зачетную книжку. Шкала оценок: «отлично», «хорошо», «удовлетворительно», «неудовлетворительно».

Студенты, не сдавшие экзамен в установленное время по уважительной причине, подтвержденной документально соответствующим документом, сдают экзамен индивидуально, в сроки, установленные отделением.

### 3.2 Перечень оценочных средств

Таблица 1

| $N_{\underline{0}}$ | Формы         | Общая характеристика формы оценивания                | Способ            |

|---------------------|---------------|------------------------------------------------------|-------------------|

| Π/                  | оценивания    |                                                      | представления     |

| П                   |               |                                                      | формы оценивания  |

|                     |               |                                                      | в фонде           |

|                     |               |                                                      | оценочных средств |

| 1                   | 2             | 3                                                    | 4                 |

| 1                   | Устный опрос  | Цель устного опроса – оценить знания и кругозор      | Тема опроса.      |

|                     | (YO)          | студента, умение логически построить ответ,          | Вопросы для       |

|                     |               | владение монологической и диалогической речью,       | индивидуального   |

|                     |               | уровень развития мышления. Обучающая функция         | опроса.           |

|                     |               | устного опроса состоит в выявлении вопросов,         |                   |

|                     |               | которые по каким-то причинам оказались               |                   |

|                     |               | недостаточно осмысленными в ходе учебных занятий     |                   |

|                     |               | и при подготовке к зачёту или экзамену, и            |                   |

|                     |               | определении способов коррекции пробелов в знаниях    |                   |

|                     |               | и умениях студентов. Устный опрос может              |                   |

|                     |               | осуществляться в различных видах (индивидуальный.    |                   |

|                     |               | групповой, фронтальный, комбинированный)             |                   |

|                     |               |                                                      |                   |

| 2                   | Письменный    | Письменный ответ – важнейший способ точного,         | Варианты заданий  |

|                     | onpoc         | лаконичного, связного изложения мысли,               |                   |

|                     | ( <b>ПО</b> ) | собственной точки зрения. Письменная проверка        |                   |

|                     | ,             | используется во всех видах контроля и                |                   |

|                     |               | осуществляется как в аудиторной, так и во            |                   |

|                     |               | внеаудиторной работе. Письменные работы могут        |                   |

|                     |               | включать: диктанты, тесты, контрольные работы,       |                   |

|                     |               | эссе, рефераты, курсовые работы, отчеты по           |                   |

|                     |               | практическим занятиям, отчеты по учебно-             |                   |

|                     |               | исследовательской работе студентов.                  |                   |

| 3                   | Контрольная   | Письменные контрольные работы – одно из средств      | Варианты заданий. |

|                     | работа        | опроса, которое осуществляется с целью проверки      | •                 |

|                     | (KP)          | знаний всех студентов по данной теме;                |                   |

|                     | ()            | стимулирования непрерывной систематической           |                   |

|                     |               | работы студентов; формирования умений в              |                   |

|                     |               | письменном виде сжато излагать материал.             |                   |

|                     |               | Различают несколько видов контрольных работ:         |                   |

|                     |               | обязательные, домашние, текущие, экзаменационные,    |                   |

|                     |               | consurements, domainme, renymere, onsumental months, |                   |

| 4 | Tecm<br>(T)                                                | практические, фронтальные и индивидуальные. Контрольные работы проводятся, как правило, после завершения изучения темы или раздела (модуля) и содержат задания различных типов и уровней сложности. Во время проверки и оценки контрольных письменных работ проводится анализ результатов выполнения, выявляются типичные ошибки, а также причины их появления.  Педагогический тест определяется как система параллельных стандартизированных заданий равномерно возрастающей трудности, специфической формы, позволяющая качественно и эффективно измерить уровень и оценить структуру подготовленности обучающихся. По степени однородности задач тесты делятся на: гомогенные, предназначенные для контроля знаний и умений по одной дисциплине; гетерогенный, предназначенный для измерения | Образцы и<br>варианты тестовых<br>заданий. Критерии<br>оценки. Шкала<br>оценивания.<br>Формы оценочных<br>листов. |

|---|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 5 | Практические<br>(лабораторны<br>е) занятия<br>(ПР)<br>(ЛР) | дисциплинам, междисциплинарным курсам и профессиональным модулям.  Практическое задание - это задание, с помощью которых у студентов формируются и развиваются правильные практические действия, четкое и ясное задание по конкретной предметной области, требующее однозначно определяемого ответа или выполнения определенного алгоритма действий.                                                                                                                                                                                                                                                                                                                                                                                                                                             | Темы практических заданий и отчеты о ПР(ЛР)                                                                       |

|   |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                   |

3.3 Формы и методы оценивания

| -                                                                                                                                                         | Формы и методы контроля |                                                               |                   |                                                                     |                |                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------|-------------------|---------------------------------------------------------------------|----------------|--------------------------|

| Элемент учебной дисциплины                                                                                                                                | Текущі                  | ий контроль                                                   | Рубежні           | ый контроль                                                         | Промежуточна   | я аттестация             |

| , , ,                                                                                                                                                     | <b>Форма</b> контроля   | Проверяемые<br>ПК, ОК, У, 3                                   | Форма<br>контроля | Проверяемые ПК, ОК, У, 3                                            | Форма контроля | Проверяемые ПК, ОК, У, 3 |

| Раздел 1 Арифметические основы цифровой схемотехники                                                                                                      |                         |                                                               | TECT№1            | <b>У1.,У2. ,31.,32,</b><br>ОК.1, ОК.2,<br>ОК3, ОК4, ОК5,<br>ОК6,ОК9 |                |                          |

| Тема 1.1. Формы представления числовой информации в цифровых устройствах                                                                                  | УО,                     | У1.,У2. ,31.,32,<br>ОК 1,2                                    |                   |                                                                     |                |                          |

| Кодирование целых, дробных и смешанных чисел в различных системах счисления                                                                               | ПР №1                   | <b>Y1.,Y2.,31</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9 |                   |                                                                     |                |                          |

| Кодирование положительных и отрицательных двоичных чисел в прямом, обратном, дополнительном и модифицированном кодах со знаковым и без знакового разряда. | ПР №2                   | <b>Y2, 31-32</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9  |                   |                                                                     |                |                          |

| Тема 1.2.<br>Арифметических операций с кодированными числами                                                                                              | УО                      | У2, 31-32<br>ОК 1,2                                           |                   |                                                                     |                |                          |

| Выполнение арифметических операций с многоразрядными двоичными кодированными числами со знаковым и без знакового разряда.                                 | ПР№3                    | <b>Y2, 31-32</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9  |                   |                                                                     |                |                          |

| Раздел 2 Логические основы цифровой схемотехники                                                                                                          |                         |                                                               | TECT№2            | У1.,У2. ,31.,32,                                                    |                |                          |

|                                                                       |              |                                                                       |    | ОК.1, ОК.2,<br>ОК3, ОК4, ОК5,<br>ОК6,ОК9<br>ПК1.1 |  |

|-----------------------------------------------------------------------|--------------|-----------------------------------------------------------------------|----|---------------------------------------------------|--|

| Тема 2.1<br>Функциональная<br>логика                                  | УО           | <b>Y2, 31-32</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9          |    |                                                   |  |

| Преобразование логических выражений                                   | ПР № 4       | У2, 31-32<br>ОК 1,2                                                   |    |                                                   |  |

| Тема 2.2<br>Основы синтеза<br>цифровых логических<br>устройств        | УО           | <b>У2, 31-32</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9<br>ПК1.1 |    |                                                   |  |

| Построение схем цифровых логических устройств методом синтеза.        | УО, ПР<br>№5 | У2, 31-32<br>ОК 1,2<br>ПК1.1                                          |    |                                                   |  |

| Тема 2.3 Цифровые интегральные микросхемы                             | УО           | <b>У2, 31-32</b><br>ОК.1, ОК.2,<br>ОК3, ОК4, ОК5,<br>ОК6,ОК9<br>ПК1.1 |    |                                                   |  |

| Раздел 3 Последовательностные цифровые устройства — цифровые автоматы |              |                                                                       | ПО | OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9          |  |

| Тема 3.1 Цифровые триггерные схемы                                    | ЛР №1,       | <b>У2, 31-32</b><br>OK.1, OK.2,<br>OK3, OK4, OK5,<br>OK6,OK9<br>ПК1.1 |    |                                                   |  |

| Тема 3.2 Цифровые счётчики импульсов                                  | ЛР №2        | У2, 31-32<br>ОК 1,2<br>ПК1.1                                          |    |                                                   |  |

| Тема 3.3 Регистры                                         | ЛР №3   | <b>У2, 31-32</b><br>ОК.1, ОК.2,<br>ОК3, ОК4, ОК5,<br>ОК6,ОК9<br>ПК1.1 |    |  |  |

|-----------------------------------------------------------|---------|-----------------------------------------------------------------------|----|--|--|

| Раздел 4 Комбинационные                                   |         |                                                                       |    |  |  |

| цифровые устройства                                       | #P 14.5 |                                                                       |    |  |  |

| Тема 4.1 Шифраторы и дешифраторы                          | ЛР №5   | У2, 31-32<br>ОК 1,2<br>ПК1.1                                          |    |  |  |

| Тема 4.2 Преобразователи                                  |         |                                                                       |    |  |  |

| кодов                                                     |         |                                                                       |    |  |  |

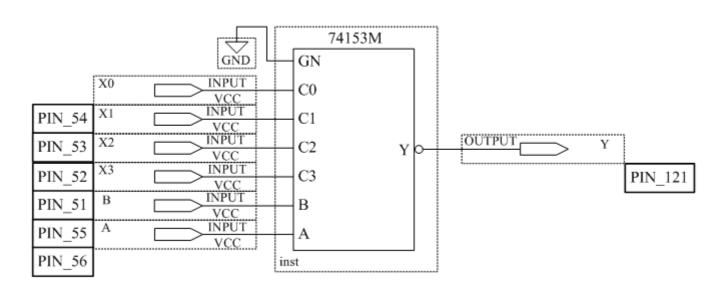

| Тема 4.3 Мультиплексоры и                                 | ЛР №6   | У2, 31-32                                                             |    |  |  |

| демультиплексоры                                          |         | ОК 1,2<br>ПК1.1                                                       |    |  |  |

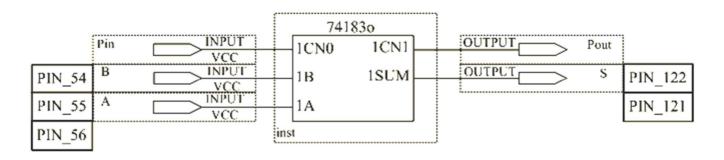

| Тема 4.4 Комбинационные двоичные сумматоры                | ЛР №7   | У2, 31-32<br>ОК 1,2<br>ПК1.1                                          |    |  |  |

| Тема 4.5 Цифровые компараторы                             |         | У2, 31-32<br>ОК 1,2<br>ПК1.1                                          |    |  |  |

| Раздел 5 Цифровые запоминающие устройства                 |         |                                                                       | ПО |  |  |

| Тема 5.1 Классификация и параметры запоминающих устройств |         |                                                                       |    |  |  |

| Тема 5.2 Оперативные запоминающие устройства              |         |                                                                       |    |  |  |

| Тема 5.3 Постоянные                                       |         |                                                                       |    |  |  |

| запоминающие устройства                                   |         |                                                                       |    |  |  |

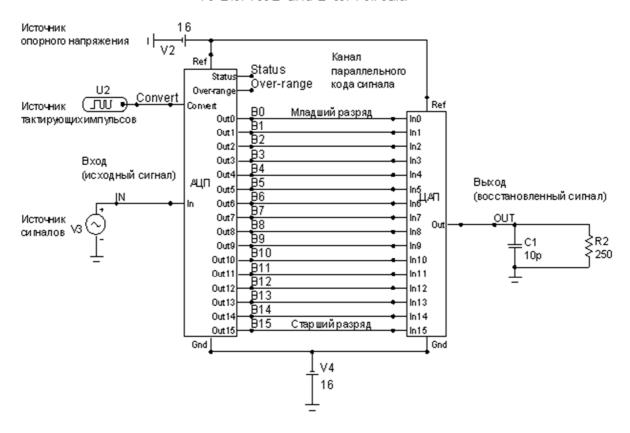

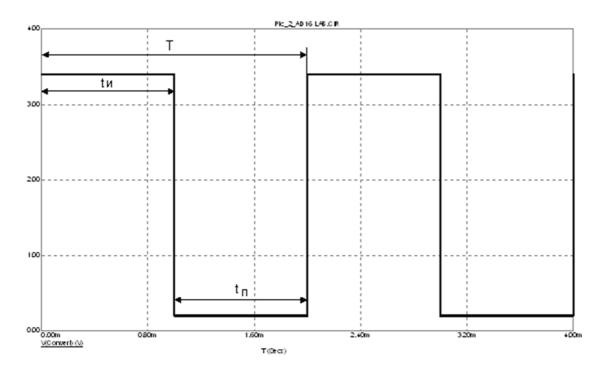

| Раздел 6 Аналого-цифровые                                 |         |                                                                       |    |  |  |

| (АЦП) и цифро-аналоговые                                  |         |                                                                       |    |  |  |

| преобразователи (ЦАП)<br>информации                       |         |                                                                       |    |  |  |

| Тема 6.1 Цифро-аналоговые                                 |         |                                                                       |    |  |  |

| преобразователи (ЦАП) кода в                              |         |                                                                       |    |  |  |

| напряжение                                      |       |                                    |  |         |                                                                       |

|-------------------------------------------------|-------|------------------------------------|--|---------|-----------------------------------------------------------------------|

| Тема 6.2 Аналого-цифровые (АЦП) преобразователи | ЛР №7 | <b>Y2, 31-32</b><br>OK.1, OK.2,    |  |         |                                                                       |

| информации                                      |       | ОК3, ОК4, ОК5,<br>ОК6,ОК9<br>ПК1.1 |  |         |                                                                       |

| Раздел 7 Микропроцессоры и микропроцессорные    |       |                                    |  |         |                                                                       |

| устройства                                      |       |                                    |  |         |                                                                       |

| Тема 7.1 Общие сведения о                       |       |                                    |  |         |                                                                       |

| микропроцессорах и                              |       |                                    |  |         |                                                                       |

| микропроцессорных системах                      |       |                                    |  |         |                                                                       |

| Тема 7.2 Микропроцессорные                      |       |                                    |  |         |                                                                       |

| устройства                                      |       |                                    |  |         |                                                                       |

| Материал по всему курсу<br>дисциплины           |       |                                    |  | Экзамен | <b>У2, 31-32</b><br>ОК.1, ОК.2,<br>ОК3, ОК4,<br>ОК5, ОК6,ОК9<br>ПК1.1 |

### 4. Задания для оценки освоения учебной дисциплины

### 4.1. Задания для текущего контроля

### Вопросы для проведения устного опроса УО

# По теме 1.1 «Формы представления числовой информации в цифровых устройствах»

- 1. По каким причинам наибольшее распространение в ЭВМ получила двоичная система счисления?

- 2. Какие системы счисления используются в ЭВМ?

- 3. Поясните сущность позиционных систем счисления.

- 4. Сформулируйте общие правила перевода целых и дробных чисел из одной системы счисления в другую.

- 5. Форма числа с фиксированной запятой.

- 6. Форма числа с плавающей запятой.

### По теме 1.2 «Арифметических операций с кодированными числами»

- 1. Изображение числа в прямом коде.

- 2. Изображение числа в обратном коде.

- 3. Изображение числа в дополнительном коде.

- 4. Почему в ЭВМ не выполняется операция вычитания чисел в непосредственном виде.

### По теме 2.1 «Функциональная логика»

- 1. Определите понятие логической переменной и логической функции.

- 2. Сколько логических функций существует для n логических переменных?

- 3. Какими свойствами обладают логические функции дизъюнкции, конъюнкции и отрицания?

- 4. Каким образом представляется логическая функция?

- 5. Приведите соотношения, отражающие основные законы алгебры логики.

- 6. Сформулируйте правила образования ДСНФ.

- 7. Сформулируйте правила образования КСНФ.

### Практические работы для проведения текущего контроля (ПР)

### Практическое занятие №1 Кодирование целых, дробных и смешанных чисел в различных системах счисления

*Цель*: научиться кодировать числа в различных системах счисления.

Оборудование: раздаточный материал.

### Краткие теоретические сведения

Арифметические действия, выполняемые в двоичной системе, подчиняются тем же правилам, что и в десятичной системе. Только в двоичной системе счисления перенос единиц в старший разряд возникает чаще, чем в десятичной. Вычитание многоразрядных двоичных чисел производится с учетом возможных заёмов из старших разрядов. Действия умножения и деления в двоичной арифметике можно выполнять по общепринятым для позиционных систем правилам.

Сложение двоичных чисел. Способ сложения столбиком такой же, как и для десятичного числа. То есть, сложение выполняется поразрядно, начиная с младшего. Если получается больше 1, то записывается 0 и 1 добавляется к старшему разряду. Вот так выглядит таблица сложения в двоичной системе:

Таблица 1 Сложение двоичных чисел

| 0+0=0 | 0+1=1                             |

|-------|-----------------------------------|

| 1+0=1 | 1+1=10 (перенос в старший разряд) |

Пример 1: 10011 + 10001.

|   | 1 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|

|   | 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

Переведём все три числа в десятичную систему и проверим правильность сложения.

$$10011 = 1*2^4 + 0*2^3 + 0*2^2 + 1*2^1 + 1*2^0 = 16 + 2 + 1 = 19$$

$10001 = 1*2^4 + 0*2^3 + 0*2^2 + 0*2^1 + 1*2^0 = 16 + 1 = 17$

$100100 = 1*2^5 + 0*2^4 + 0*2^3 + 1*2^2 + 0*2^1 + 0*2^0 = 32 + 4 = 36$

$17 + 19 = 36$  верное равенство

**Вычитание** двоичных чисел. Вычитание выполняется поразрядно и если в разряде не хватает единицы, то она занимается в старшем.

Пример 2:

|   | 1 | 1 | 0 | 1 |

|---|---|---|---|---|

| - |   | 1 | 1 | 0 |

|   |   | 1 | 1 | 1 |

Первый разряд. 1 - 0 = 1. Записываем 1.

Второй разряд 0 -1. Не хватает единицы. Занимаем её в старшем разряде. Единица из старшего разряда переходит в младший, как две единицы (потому что старший разряд представляется двойкой большей степени ) 2-1 =1. Записываем 1.

Третий разряд. Единицу этого разряда мы занимали, поэтому сейчас в разряде 0 и есть необходимость занять единицу старшего разряда. 2-1 =1. Записываем 1.

Проверим результат в десятичной системе:

$$1101 - 110 = 13 - 6 = 7$$

(111) Верное равенство.

**Умножение в двоичной системе счисления.** Таблица умножения для двоичных чисел ещё проще, чем для сложения.

Таблица 1 Умножение двоичных чисел

| 0*0=0 | 0*1=0 |

|-------|-------|

| 1*0=0 | 1*1=1 |

Для того, чтобы умножить двоичное число на 2 (десятичная двойка это 10 в двоичной системе) достаточно к умножаемому числу слева приписать один ноль.

Пример 3: 10101 \* 10 = 101010

Проверка.

$$10101 = 1*2^4 + 0*2^3 + 1*2^2 + 0*2^1 + 1*2^0 = 16 + 4 + 1 = 21$$

$$101010 = 1*2^5 + 0*2^4 + 1*2^3 + 0*2^2 + 1*2^1 + 0*2^0 = 32 + 8 + 2 = 42$$

$$21*2 = 42$$

Умножение - это ряд последовательных сдвигов. Общее правило таково: как и для десятичных чисел, умножение двоичных выполняется поразрядно. И для

каждого разряда второго множителя к первому множителю добавляется один ноль справа. Пример 4:(пока не столбиком):

1011 \* 101 Это умножение можно свести к сумме трёх поразрядных умножений:

1011 \* 1 + 1011 \* 0 + 1011 \* 100 = 1011 + 101100 = 110111 В столбик это же самое можно записать так:

|   |   | 1 | 0 | 1 | 1 |

|---|---|---|---|---|---|

|   | * |   | 1 | 0 | 1 |

|   |   | 1 | 0 | 1 | 1 |

| + | 0 | 0 | 0 | 0 |   |

| 1 | 0 | 1 | 1 |   |   |

| 1 | 1 | 0 | 1 | 1 | 1 |

### Проверка:

101 = 5 (десятичное) 1011 = 11 (десятичное)

110111 = 55 (десятичное) 5\*11 = 55 верное равенство

### Порядок выполнения

- 1. Выполнить арифметическую операцию сложения в двоичной системе.

- 2. Выполнить арифметическую операцию вычитания в двоичной системе.

- 3. Выполнить арифметическую операцию умножения в двоичной системе.

- 4. Ответить на контрольные вопросы.

## Содержание отчёта

- 1. Номер, название и цель практической работы.

- 2. Сложение, вычитание и умножение чисел в двоичной системе.

- 3. Вывод.

### Контрольные вопросы

- 1. С какого разряда начинается сложение?

- 2. В каком разряде занимается единица при вычитании?

- 3. Как производится перевод чисел из десятичной системы в двоичную.

### Практическое занятие №2

# **Кодирование положительных и отрицательных двоичных чисел в прямом, обратном,**

# дополнительном и модифицированном кодах со знаковым и без знакового разряда

*Цель:* научиться кодировать числа в различных кодах.

Оборудование: раздаточный материал.

### Краткие теоретические сведения

Минимизация (упрощение) булевой функции — это такие тождественные преобразования её формулы, которые приводят к предельному уменьшению числа вхождений аргументов. В результате преобразований получается минимальная форма. Если ограничиться функцией четырех переменных аргументов, то для минимизации эффективней пользоваться картами Карно. Для этого достаточно научиться находить на карте группы единиц, которым соответствуют простые импликанты. Правила их нахождения просты:

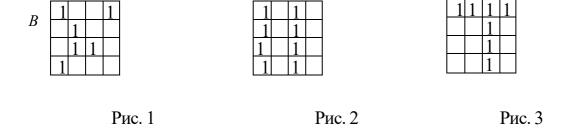

а) два минтерма склеиваются, если они являются соседними, т. е. расположенными рядом (но не на диагонали) либо на концах строки или столбца. На рис. 1 обведены склеивающиеся минтермы 11 и 15, 3 и 11; склеиваются также минтермы 4и12,8и12;

б) четыре единицы на карте объединяются и образуют одну конъюнкцию, если они расположены в строку или столбец, а также квадратом. На рис. 2 слева единицы дают конъюнкцию AC, остальные - AC. На рис. 3 единицы, расположенные в строку, образуют конъюнкцию BD, в колонку - AC. На рис. 4 единицы расположены квадратами: AB и AB. На рис. 5 единицы также образуют квадрат BC, в чём можно убедиться, если карту, свернуть в трубку так, чтобы её левая и правая стороны совпали. Аналогично на рис. 6 единицы дают квадрат A D, если карту свернуть в цилиндр вокруг горизонтальной оси. Если же карту свернуть в цилиндр вокруг горизонтальной и вертикальной осей одновременно, то придётся признать, что размещение четырёх единиц по углам карты также есть квадрат, образующий конъюнкцию CD (рис. 7);

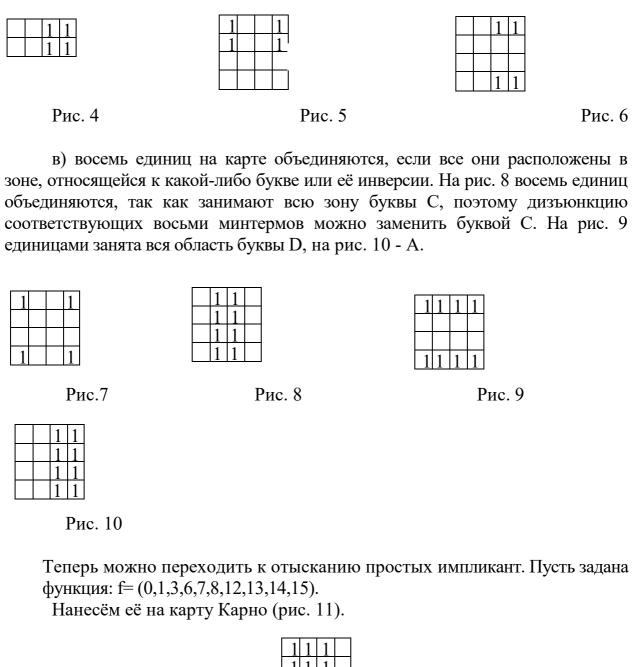

| 1 | 1 |  |

|---|---|--|

| 1 | 1 |  |

Рис.11

Начнём с нулевого минтерма. Он объединяется с минтермом  $m_1$ , поскольку единицы являются соседними. Получим первую простую импликанту ABC. Минтерм  $m_0$  является соседним и по отношению к минтерму  $m_8$ , что дает простую импликанту BCD.

Минтерм  $m_1$  объединяется и с минтермом  $m_0$  и  $m_3$ . Получаем две простые импликанты ABD и ABC. Импликанту ABC вторично не записываем. Новой является только простая импликанта ABD.

Переходим к минтерму  $m_3$ . У него также два варианта склеивания – с минтермами  $m_1$  и  $m_7$ . Новой является импликанта ACD.

Минтерм ты входит в группу единиц, расположенных квадратом.

Поэтому простой импликантой будет конъюнкция BC, но такие импликанты, как BCD и ABC не являются простыми.

Седьмой минтерм имеет три соседние единицы. Однако новых простых импликант он не даёт, поскольку объединение его с минтермом т<sub>3</sub> есть простая импликанта ACD, которая уже была записана ранее, а импликанты ABC и BCD не являются простыми, так как минтерм m<sub>7</sub> входит в квадрат единиц, также рассмотренный ранее.

Минтерм  $m_{12}$  входит в квадрат единиц, дающих конъюнкцию AB. Это новая простая импликанта. Кроме того, минтерм  $m_{12}$  является соседним по отношению к минтерму  $m_8$ , что даёт новую простую импликанту ACD. Минтерм  $m_{13}$  новых импликант не даёт. Минтерм  $m_{14}$  входит в два квадрата: AB и BC. Новых импликант нет. То же самое относится к минтерму  $m_{15}$ .

Таким образом, найдены все простые импликанты, дизъюнкция которых образует сокращённую дизъюнктивную нормальную форму:

$$F = ABC + BCD + ABD + ACD + BC + ACD + AB$$

### Порядок выполнения

- 1. Минимизировать логические функции методом карт Карно.

- 2. Составить схему.

- 3. Ответить на контрольные вопросы.

### Содержание отчёта

- 1. Номер, название и цель практической работы.

- 2. Схемы карт Карно.

- 3. Вывод.

### Контрольные вопросы

- 1. Поясните принцип минимизации.

- 2. Что получается в результате минимизации.

### Практическое занятие №3

Выполнение арифметических операций с многоразрядными двоичными кодированными числами со знаковым и без знакового разряда

**Цель:** научиться выполнять арифметические операции над кодированными числами.

Оборудование: раздаточный материал.

### Краткие теоретические сведения

### Прямой, обратный и дополнительный коды

При проектировании вычислительных устройств необходимо решить вопрос о способе представления в машине положительных и отрицательных чисел и о признаке переполнения разрядной сетки. Указанный вопрос решается применением специальных колов для представления чисел. При помощи этих кодов операция вычитания (или алгебраического сложения) сводится к арифметическому сложению. В результате упрощаются арифметические устройства машин.

Для представления двоичных чисел в машине применяют прямой, обратный и дополнительный коды. Во всех этих кодах предусматривается дополнительный разряд для представления знака числа, причем знак «+» кодируется цифрой 0, а знак «— » - цифрой 1.

Положительные числа при прямом, обратном и дополнительном кодах имеют один и тот же вид, а отрицательные — различный.

Прямой код (G)пр двоичного числа  $G=\pm 0, \gamma 1, \gamma 2, \ldots, \gamma n$  ( $\gamma i=1$  или 0) определяется условиями:

$$G$$

при  $G \ge 0$

$(G)$ пр =  $(1 - G)$  при  $G \le 0$

Положительное двоичное число с запятой, фиксированной перед старшим разрядом,

$$G+=+0, \gamma 1, \gamma 2, \ldots, \gamma n$$

в прямом коде представляется в виде:

$$(G+) \pi p = 0, \gamma 1, \gamma 2, ..., \gamma n (1)$$

Аналогично отрицательное двоичное число:

$$G = -0, \gamma 1, \gamma 2, ..., \gamma n (1a)$$

в прямом коде представляется в виде:

(G-) πp = 1,

$$\gamma$$

1,  $\gamma$ 2, ...,  $\gamma$ n (2)

Способы представления чисел (1) и (2) называются прямым кодом соответственно положительных и отрицательных двоичных чисел.

# Сложение и вычитание в прямом, обратном и дополнительном кодах

Сложение в прямом коде чисел, имеющих одинаковые знаки, выполняется достаточно просто. Мантиссы складываются и сумме присваивается код знака слагаемых. Значительно более сложной является операция алгебраического сложения в прямом коде чисел с раз-

личными знаками. В этом случае приходится определять большое по модулю число, производить вычитание мантисс и присваивать разности знак большего (по модулю) числа. Таким образом, если положительные и отрицательные числа представлены в прямом коде, операции над кодами знаков и мантиссами выполняются раздельно.

Операция вычитания (алгебраического сложения) сводится к операции простого арифметического сложения при помощи обратного и дополнительного кодов, используемых для представления отрицательных

чисел в машине. При этом операция сложения распространяется и на разряды знаков, рассматриваемых как разряды целой части числа.

Чтобы представить двоичное отрицательное число (1a) в обратном коде, нужно поставить в знаковый разряд единицу, а во всех других разрядах заменить единицы нулями, а нули — единицами:

(G-)

$$obp = 1, \sigma 1, \sigma 2, ..., \sigma n$$

(3)  $\sigma i = 1 \pi \rho u \gamma i = 0 u \sigma i = 0 \pi \rho u \gamma i = 1.$

При записи отрицательного числа в дополнительном коде ставят единицу в разряд знака, а цифровую часть числа заменяют дополнением модуля числа до целой единицы.

Отрицательное число G- = - 0,  $\gamma 1, \ \gamma 2, \ \dots$ ,  $\gamma n$  в дополнительном коде имеет вид:

(G-) доп = 1,

$$\epsilon$$

1,  $\epsilon$ 2, ...,  $\epsilon$  n (4) где 0,  $\epsilon$ 1,  $\epsilon$ 2, ...,  $\epsilon$  n = 1 - 0,  $\gamma$ 1,  $\gamma$ 2, ...,  $\gamma$ n (4a)

Установим связь между самим отрицательным числом G- и числами (G-)обр и (G-)доп, представляющими его обратный и дополнительный коды.

Вычитая (1а) из (3), имеем:

(G-) обр - G- = 1,

$$\sigma$$

1,  $\sigma$  2, ...,  $\sigma$  n – ( - 0,  $\gamma$ 1,  $\gamma$ 2, ...,  $\gamma$ n) = 1,11...1 = 2 – 2- n (так как  $\sigma$ i +  $\gamma$ i = 1)

Следовательно,

$$(G-) obp = G- + 2 - 2-n (4b)$$

Вычитая (1а) из (4), имеем:

(G-) доп - G- = 1,

$$\epsilon$$

1,  $\epsilon$  2, ...,  $\epsilon$  n - ( - 0,  $\gamma$ 1,  $\gamma$ 2, ...,  $\gamma$ n) (5)

Учитывая (4а), получаем:

$$(G-)$$

доп =  $G-+2$   $(5a)$

Из (5) и (5а) следует:

$$(G-)$$

доп =  $(G-)$  обр + 2-n

где n — число разрядов в числе. Таким образом, дополнительный код может быть получен из обратного путем добавления к нему единицы младшего разряда.

Рассмотрим представление нуля. В процессе вычислений могут возникнуть «положительный» и «отрицательный» нули:

Представление «положительного» нуля одинаково для прямого, обратного и дополнительного кодов:

$$(+0) \pi p = 0.00...0$$

Отрицательный нуль изображается: в прямом коде

$$(-0) \text{ np} = 0.00...0$$

в обратном коде

$$(-0)$$

of  $p = 1,11...1$

в дополнительном коде

$$(-0)$$

доп =  $1,11...1 + 2-n = 0,00...0$

так как перенос из разряда знака теряется.

Используя обратный или дополнительный код, можно операции вычитания и сложения чисел различных знаков свести к арифметическому сложению кодов чисел.

Рассмотрим использование обратного кода при алгебраическом сложении двух двоичных чисел G и Q, когда одно из них или оба числа отрицательны. Для этого случая может быть сформулировано следующее правило (предполагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием обратного кода положительные слагаемые представляются в прямом коде, а отрицательные - в обратном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса прибавляется к младшему разряду суммы кодов (такой перенос называется круговым или циклическим). В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в обратном коде, если она отрицательна.

Рассмотрим теперь использование дополнительного кода для алгебраического сложения. Приведем соответствующее правило (полагаем, что модуль алгебраической суммы меньше единицы).

При алгебраическом сложении двух двоичных чисел с использованием дополнительного кода положительные слагаемые представляются в прямом коде, а отрицательные — в дополнительном и производится арифметическое суммирование этих кодов, включая разряды знаков, которые при этом рассматриваются как разряды целых единиц. При возникновении переноса из разряда знака единица переноса отбрасывается. В результате получается алгебраическая сумма в прямом коде, если эта сумма положительна, и в дополнительном коде, если эта сумма отрицательна.

В самом деле, если G- < 0 и Q- < 0 , то согласно (4b):

$$(G-)$$

доп  $+ (Q-)$  доп  $= G-+2+G-+2=2+(G-+Q-+2)$

Так как -1 < G-+Q-< 0, то величина, стоящая в скобках, меньше двух, но больше единицы. Двойка, стоящая вне скобки, образует перенос из разряда знака, который будет отброшен. В результате получаем:

$$(G+)$$

пр +  $(Q-)$  доп =  $(G++Q-)+2$

Если при этом 0 < G+ + Q- < 1, то стоящая вне скобки двойка дает единицу переноса из разряда знака, которая отбрасывается. При этом получаем:

$$(G+)$$

пр  $+$   $(Q-)$  доп  $=$   $(G++Q-)$  пр  $(G++Q->0)$

Если же -1 < G++Q-<0, то (G++Q-)+2<2 и переноса из разряда знака не возникает. В этом случае:

$$(G+)$$

пр  $+$   $(Q-)$  доп  $=$   $(G++Q-)$  доп  $(G++Q-<0)$ .

Применение дополнительного или обратного кода для представления отрицательных чисел упрощает операцию алгебраического сложения. Алгебраическое сложение чисел с разными знаками заменяется арифметическим сложением кодов, при этом автоматически получается код знака результата. Однако остается нерешенным вопрос о выработке признака переполнения разрядной сетки.

При сложении кодов теряется единица переноса из разряда целых единиц и результат ошибочно воспринимается как положительное число, меньшее единицы.

Отметим, что при алгебраическом сложении двух чисел G и Q, каждое из которых по модулю меньше единицы, может возникнуть переполнение разрядной сетки, но при этом модуль получаемой суммы всегда меньше двух. Это обстоятельство облегчает построение кодов, по виду которых можно судить о переполнении разрядной сетки.

Для получения признака переполнения разрядной сетки применяют модифицированные прямой, дополнительный и обратный коды. Эти коды отличаются от ранее рассмотренных кодов тем, что для представления знака используются два разряда.

При этом знак плюс обозначается 00, а знак минус — 11. При алгебраическом сложении чисел знаковые разряды рассматриваются как разряды целой части числа.

При возникновении переноса единицы из старшего разряда знака эта единица отбрасывается, если отрицательные числа представляются модифицированным дополнительным кодом, или производится циклический перенос в младший разряд мантиссы, если отрицательные числа изображаются модифицированным обратным кодом.

При алгебраическом сложении на переполнение разрядной сетки (модуль алгебраической суммы больше единицы) указывает несовпадение цифр в знаковых разрядах. Комбинации 01 в знаковых разрядах соответствует положительное число, а комбинации 10 — отрицательное число.

В этих случаях модуль суммы:

$$1 \le |\mathbf{x}| < 2$$

Отметим также особенности нормализации и выполнения сдвига для отрицательных чисел, представленных в дополнительном (обратном) коде.

У нормализованного положительного или отрицательного числа с мантиссой, изображаемой в прямом коде, цифра в старшем S-ичном разряде мантиссы должна быть отлична от нуля. Для отрицательных мантисс, представленных в обратном или дополнительном коде, условие нормализации  $|\mathbf{q}| \ge 1/S$  выполняется, если цифра в старшем S-ичном разряде мантиссы есть нуль.

В случае чисел с плавающей запятой комбинации 01 и 10 в знаковых разрядах мантиссы указывают на нарушение нормализации влево, а комбинации цифр 00 и 1  $\sigma s1$  ( $\sigma s1 \neq 0$ ) в младшем знаковом разряде и старшем S-ичном цифровом разряде мантиссы сигнализируют о нарушении

нормализации вправо. Для восстановления нормализации производится сдвиг мантиссы вправо (или влево) на нужное число разрядов, при этом порядок увеличивается (уменьшается) на соответствующее число единиц,

Если отрицательные числа представляются дополнительном (обратном) сдвиг производится особым коде, ПО правилам («модифицированный сдвиг»), с тем чтобы результате сдвига дополнительного (обратного) кода числа х на т S-ичных разрядов получился дополнительный (обратный) код числа Smx или S-mx соответственно для сдвига влево или вправо.

При модифицированном сдвиге дополнительного (обратного) кода вправо в освобождающиеся старшие разряды мантиссы записываются единицы, а при сдвиге влево единицы записываются в освобождающиеся младшие разряды.

### Деление в прямом, обратном и дополнительном кодах

Деление в вычислительной машине обычно сводится к выполнению последовательности вычитаний делителя сначала из делимого, а затем из образующихся в процессе деления частичных остатков и сдвига частичных остатков на один разряд влево.

Необходимо отметить, что в машинах, оперирующих над числами с запятой, фиксированной перед старшим разрядом, деление возможно только в одном случае, если делимое по модулю меньше делителя. В противном случае частное превышает единицу и выходит за пределы разрядной сетки числа. Если в результате вычитания выясняется, что делимое или очередной частичный остаток больше или равны делителю, то в очередной разряд частного записывается единица и полученный в результате вычитания частичный остаток сдвигается влево на один разряд. Если в результате вычитания выясняется, что делимое или очередной частичный остаток меньше делителя, то в очередной разряд частного записывается нуль, к разрядности добавляется полученной делитель, чтобы предыдущий частичный остаток, и результат сдвигается влево на один Метод выполнения деления, когда случае получения В остатка при вычитании (частичный остаток отрицательного делимого) к нему прибавляется делитель, называется методом деления с восстановлением остатка.

Рассмотрим пример деления с восстановлением остатка (см. таблицу). Для выполнения операции вычитания будем использовать дополнительный код. Деление с восстановлением остатка требует в наиболее неблагоприятном случае трёх тактов для формирования одного разряда частного: такта вычитания, такта сложения и такта сдвига.

Рассмотренный метод носит название *деления с восстановлением остатка*.

Недостатком этого метода является необходимость введения специального третьего такта для восстановления остатка, который значительно замедляет ход вычисления.

Обычно в вычислительных машинах для деления широко используется другой метод, называемый методом выполнения деления без восстановления остатка. Этот метод основан на прямом копировании действий при ручном делении («в столбик»).

При этом методе, если результат вычитания получился отрицательный, частичный остаток не восстанавливается путём прибавления делителя, а на следующем шаге деления вместо вычитания делимого производится его прибавление к частичному остатку. Если результат при этом остался отрицательным, то в очередную цифру частного записывается нуль и на следующем шаге также выполняется сложение. Если результат сложения получился положительным, то в очередной разряд частного записывается единица и на следующем шаге производится вычитание.

Можно показать, что частичные остатки при делении без восстановления остатка получаются такими же, как и остатки после сдвига восстановленного остатка при делении с восстановлением остатка.

Действительно, поскольку сдвиг частичного остатка на один разряд влево эквивалентен умножению его на два, получим:

$$2a - b = 2(a - b) + b$$

где а – частичный остаток; b – делитель.

Аналогично:

$$2^{n}a = \{...\{(a-b)2+b]2+b\}2+...+b\}$$

Деление без восстановления остатка всегда требует для получения одной цифры частного только двух тактов: такта сложения или вычитания и такта сдвига. Тем самым скорость вычисления этим методом оказывается выше чем в методе деления с восстановлением остатка.

Деление правильных дробей выполняется также, как деление целых чисел. Разница же заключается в том, что делимое имеет, как правило, такую же длину, как и делитель. Однако можно предположить, что делимое имеет ещё п младших разрядов, равных 0. Тогда становится ясно, что алгоритм деления дробей ничем не отличается от алгоритма деления целых чисел.

Исходя из рассмотренных методов деления в вычислительных машинах наиболее скоростной и простой метод является метод деления без восстановления остатка, так как при использовании данного метода для получения одной цифры частного необходимо выполнить всего лишь два такта, в то время как в методе с восстановлением частичного остатка для получения одной цифры частного требуется три такта.

### Практическая работа №5 Построение схем цифровых логических устройств методом синтеза.

Цель: научиться составлять аналитические выражения по табличному значению функции, строить схемы из элементарных логических элементов по заданному аналитическому выражению функции.

Продолжительность занятия 2 часа

Краткие теоретические положения:

1. Логические элементы

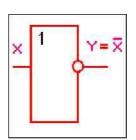

Логический элемент НЕ

Логическое ИЛИ (логическое сложение, дизъюнкция):  $\overline{y} = \overline{XI} + X2 = X1\overline{y}X2$ Таблина истинности логического ИЛИ имеет вид:

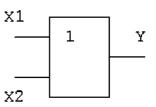

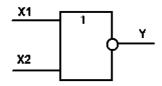

Логический ИЛИ элемент обозначается на схемах следующим образом:

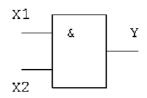

Логическое И (логическое умножение, Таблица истинности логического И имеет вид:

| X1 | I | X2 | 2 | (=X1X | 2 |

|----|---|----|---|-------|---|

| 0  | 1 | 0  | 1 | 0     |   |

| 0  | 1 | 1  | 1 | 0     |   |

| 1  | 1 | 0  | 1 | 0     |   |

| 1  | 1 | 1  | 1 | 1     |   |

Функция ИЛИ-НЕ: y = (X1+X2)

конъюнкция): y = X1X2 = X1&X2

Логический И элемент обозначается на схемах следующим образом:

Таблица истинности функции ИЛИ-НЕ имеет вид:

Логический элемент ИЛИ-НЕ обозначается на схемах следующим образом:

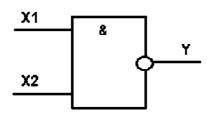

Функция И-НЕ:  $\overline{y} = (X1^{T}X2)$

Таблица истинности функции И-НЕ имеет вид:

| Х1 |       | X2 | 1.  | Y=X1X | 2 |

|----|-------|----|-----|-------|---|

| 0  | _   _ | 0  | -¦- | 1     |   |

| 0  | Ì     | 1  | I   | 1     |   |

| 1  | ĺ     | 0  | I   | 1     |   |

| 1  |       | 1  | 1   | 0     |   |

Логический элемент И-НЕ обозначается на схемах следующим образом:

- 2. Алгоритм построение логических схем.

- 1. Определить число логических переменных.

- 2. Определить количество базовых логических операций и их порядок.

- 3. Изобразить для каждой логической операции соответствующий ей вентиль.

- 4. Соединить вентили в порядке выполнения логических операций.

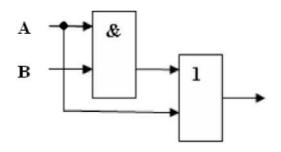

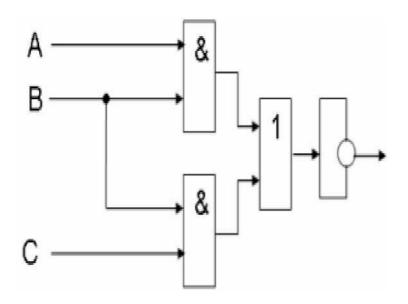

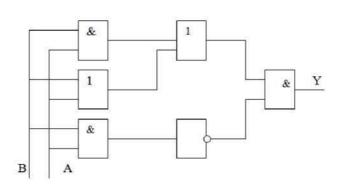

Пример 1. Составить логическую схему для логического выражения: P=A V B & A. Две переменные - A и B. Две логические

Строим схему:

Пример 2.

Постройте логическую схему, соответствующую логическому выражению E'=A&BV (BVA). Вычислить значения выражения для A=1,B=0.

Переменных две: А и В;

Логических операций три: & и две V; A&BV (BV A).

Схему строим слева направо в соответствии с порядком логических операций:

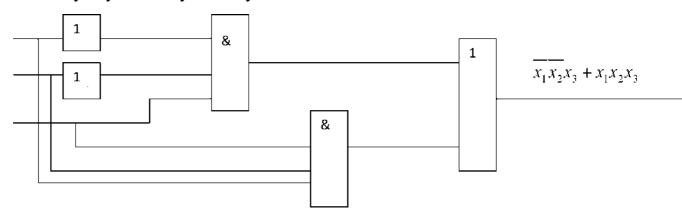

3. Составление аналитического выражения функции и построение логической схемы по табличному заданию функции.

Синтез комбинационных устройств может быть произведен по табличному заданию функции по «0» и «1». Рассмотрим для примера синтез по «1». Для всех значений аргументов  $x_b$   $x_2$ ,  $x_3$ , где функция задана как «1» берется их конъюнкция, если аргумент равен «1», если же 0 - конъюнкция их инверсий. От полученных конъюнкций берется дизъюнкция.

Например, функция от трех аргументов задана следующей таблицей:

|   | X | X | X | У |

|---|---|---|---|---|

|   | 1 | 2 | 3 |   |

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 0 |

|---|---|---|---|---|

| 4 | 0 | 1 | 1 | 0 |

| 5 | 1 | 0 | 0 | 0 |

| 6 | 1 | 0 | 1 | 0 |

| 7 | 1 | 1 | 0 | 0 |

| 8 | 1 | 1 | 1 | 1 |

Это значит, что при любых наборах аргументов ч кроме второго и последнего, аргумент у будет равен 0. Составляем для второго набора выражение:  ${}^{x} {}^{i} {}^{X_{\Gamma}} {}^{i} {}^{X_{3}}$ .

Для последнего набора:  $x_1 x_2 x_3$

Составим аналитическое выражение функции:

$$y = x_x \blacksquare x_2 \blacksquare XX + x_x \blacksquare x_2$$

Схема должна содержать инверсию сигналов x1,  $x_2$ , две схемы «И» и одну двухвходовую схему «ИЛИ»

### Последовательность выполнения:

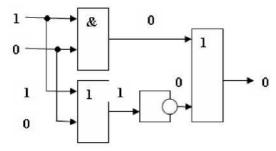

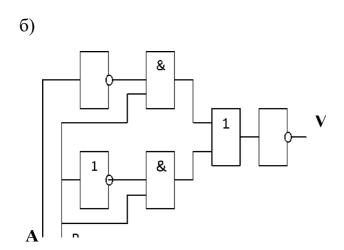

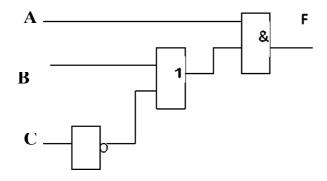

# Задание 1 Записать логическую функцию, описывающую состояние логической схемы. Составить таблицу истинности.

в)

г)

#### Задание 2

Построить логические схемы по формулам и составить таблицу истинности

- a) P= (ЛУБ)&(СУ B)

- б) P= (A&B&C)

- в) P=(X& У)у2.

- г) P=X&Уу 2.

### Отчет содержит:

- 1. Цель работы

- 2. Исходные данные и результаты выполнения заданий

### Контрольные вопросы:

- 1. Что изучает наука логика?

- 2. Перечислите и опишите известные вам формы мышления.

- 3. Опишите и составьте таблицы истинности для известных вам логических функций.

- 4. Нарисуйте условное обозначение и таблицы истинности для известных вам логических элементов.

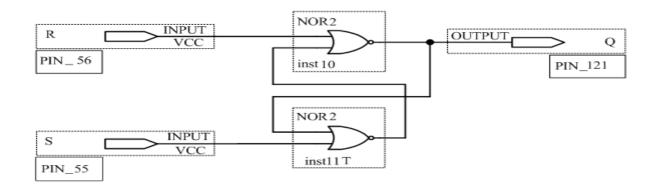

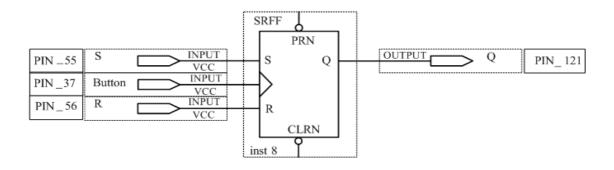

### Лабораторная работа №1

### Исследование работы интегральных триггеров на логических элементах

**Цель работы:** Целью работы является экспериментальное исследование работы различных типов <u>триггеров</u>.

### Задание к работе

### 1.Исследовать асинхронный RS-триггер

Сконфигурировать ПЛИС в соответствии с рисунком 1. Подключить к входам X0 и X1 переключатели S7 и S8, а к выходу Q светодиодный индикатор LED1. Для этого подключить входы и выходы триггера к соответствующим выводам ПЛИС.

Таблица 1. Таблица переходов для асинхронного RS триггера на элементах "ИЛИ-НЕ"

| R | S | Q(t) | Q(t+1) | Название режима работы триггера |

|---|---|------|--------|---------------------------------|

| 0 | 0 | 0    |        |                                 |

| 0 | 0 | 1    |        |                                 |

| 0 | 1 | 0    |        |                                 |

| 0 | 1 | 1    |        |                                 |

| 1 | 0 | 0    |        |                                 |

| 1 | 0 | 1    |        |                                 |

| 1 | 1 | 0    |        |                                 |

| 1 | 1 | 1    |        |                                 |

2.Исследовать синхронный асинхронный RS-триггер

Таблица 2. Таблица переходов для синхронного RS триггера

| R | S | C | Q(t) | Q(t+1) | Название режима работы триггера |

|---|---|---|------|--------|---------------------------------|

| 0 | 0 | 1 | 0    |        |                                 |

| 0 | 0 | 1 | 1    |        |                                 |

| 0 | 1 | 1 | 0    |        |                                 |

| 0 | 1 | 1 | 1    |        |                                 |

| 1 | 0 | 1 | 0    |        |                                 |

| 1 | 0 | 1 | 1    |        |                                 |

| 1 | 1 | 1 | 0    |        |                                 |

| 1 | 1 | 1 | 1    |        |                                 |

| 0 | 0 | 0 | 0    |        |                                 |

| 0 | 0 | 0 | 1    |        |                                 |

| 0 | 1 | 0 | 0    |        |                                 |

| 0 | 1 | 0 | 1    |        |                                 |

| 1 | 0 | 0 | 0    |        |                                 |

| 1 | 0 | 0 | 1    |        |                                 |

| 1 | 1 | 0 | 0    |        |                                 |

| 1 | 1 | 0 | 1    |        |                                 |

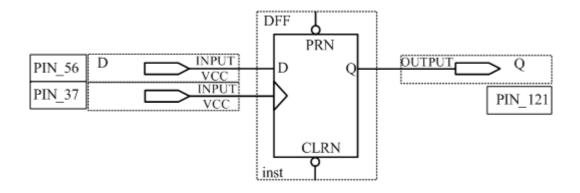

3.Исследовать D-триггер

Таблица 3. Таблица переходов для синхронного D триггера

| D | C | Q(t) | Q(t+1) |

|---|---|------|--------|

| X | 0 | 0    |        |

| X | 0 | 1    |        |

| 0 | 1 | 0    |        |

| 0 | 1 | 1    |        |

| 1 | 1 | 0    |        |

| 1 | 1 | 1    |        |

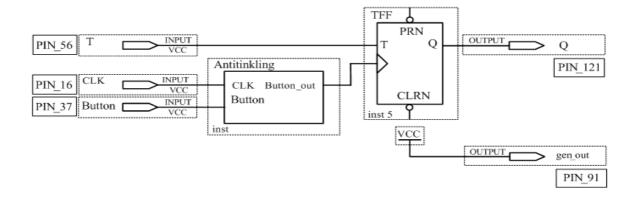

## 4 Исследовать синхронный Т-триггер

Таблица 4. Таблица переходов для синхронного Т триггера

| T | C | Q(t) | Q(t+1) | Q(t+2) | Q(t+3) | Q(t+4) | Q(t+5) |

|---|---|------|--------|--------|--------|--------|--------|

|---|---|------|--------|--------|--------|--------|--------|

| 1 | 1 | 0 |  |  |  |

|---|---|---|--|--|--|

| 1 | 1 | 1 |  |  |  |

| 0 | 1 | 0 |  |  |  |

| 0 | 1 | 1 |  |  |  |

### 5 Контрольные вопросы

- 1. Чем определяется быстродействие триггера?

- 2. Начертить схему RS-триггера на логических элементах "ИЛИ-НЕ" и пояснить принцип его работы.

- 3. Почему ЈК-триггер называется универсальным?

### Лабораторная работа №2

### Исследование функциональных схем счетчиков

<u>Цель работы:</u> Ознакомление с возможностями моделирования работы схем счетчиков.

#### 1. Основные понятия.

**Счётчик** - это электронное устройство для подсчета количества импульсов. По мере поступления входных сигналов счётчик последовательно изменяет свои состояния в определённом для данного типа счётчика порядке.

Одной из наиболее распространенных операций, выполняемых в вычислительных устройствах цифровой обработки информации является подсчет числа сигналов импульсного или потенциального вида.

Счетчики широко применяются почти во всех цифровых устройствах автоматики и вычислительной техники. В ЦВМ счетчики и используются: для подсчета шагов программы, для подсчета циклов сложения и вычитания, при выполнении арифметических операций, для преобразования кодов, в делителях частоты и распределителях сигналов и т.д.

### Классификация счетчиков по основным признакам:

- по системе счисления счетчики делятся на: двоичные, двоично-десятичные, десятичные, счетчики с основанием системы счисления неравным 2 и 10 /пересчетные схемы/.

- по реализуемой операции счетчики подразделяются на: суммирующие, вычитающие и реверсивные.

#### Основные параметры счетчиков:

- Модуль счета или коэффициент пересчета счетчика « $K_{cч}$ » характеризует число /количество/ устойчивых •состояний, в которых может находиться п-разрядный счетчик, т.е. предельное число входных сигналов, которое может быть подсчитано счетчиком.

#### 3. Задание на выполнение <u>лабораторной работы</u>.

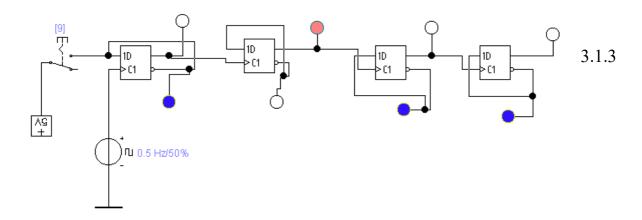

#### 3.1. Составить схему асинхронного суммирующего

#### счётчика на D-триггерах.

Пятивольтовый источник напряжения подсоединяется через переключатель к входу D1 триггера младшего (левого) разряда счетчика.

Для настройки управлением переключателя необходимо назначить клавишу для переключения данного переключателя. Для этого нужно двойным щелчком мыши кликнуть на изображении переключателя и меню настройки в форме КЕҮ указать эту клавишу.

3.1.4 Инверсный выход триггера подключить к D-входу триггера,

чтобы обеспечить работу в счётном режиме. Такое соединение провести на всех триггерах всех разрядов.

3.1.5 К прямым выходам разрядов подключить семисегментный

индикатор с дешифратором.

#### 3.2. Порядок проведения исследования работы

#### счетчиков.

3.2.1. Собрать четырёхразрядный асинхронный суммирующий счётчик на J-K триггерах. К прямым выходам триггеров подсоединить семисегментный индикатор и светодиодные индикаторы.

Исследовать и зарисовать временную диаграмму работы счётчика.

Переделать схему в вычитающий счётчик. Зарисовать временную диаграмму работы.

3.3.2 Составить схему суммирующего синхронного счётчика. В основе схемы используются J-К триггеры. Из-за того, что в библиотечных триггерах J-К есть только один J и один К вход, необходимо реализовать логику управления старшими разрядами на внешних логических элементах. На синхровходы всех разрядов подать синхроимпульсы от генератора прямоугольных импульсов. На объединённые входы J и К младшего разряда подать счетным импульс от пятивольтового источника с помощью переключателя. Зарисовать временную диаграмму и пояснить с помощью светодиодов, в какой момент

#### 4. Содержание отчета.

1. Схемы, моделирующие работу счётчиков по всем пунктам задания.

осуществляется передача счётного сигнала старшему разряду.

- 2. Временные диаграммы, поясняющие работу счётчиков.

- 3. Проанализировать работу счётчиков с помощью цифрового индикатора (по выбору).

#### 5. Контрольные вопросы.

- 1. Назначение счётчиков в вычислительных устройствах.

- 2. Признаки классификации счётчиков.

- 3. Коэффициент пересчёта счётчика.

- 4. Чем определяется максимальная частота поступления входных сигналов на счётчик?

- 5. Какое свойство Ј-К триггеров позволяет построить на их основе синхронные счётчики?

- 6. Какое устройство позволяет построить реверсивный счётчик?

- 7. Поясните временную диаграмму работы счётчика Джонсона.

# Лабораторная работа №3

#### Исследование функциональных схем регистров

**Цель работы:** экспериментальное исследование работы цифровых регистров различных типов.

## Подготовка к лабораторной работе

- 1. По конспекту лекций изучить работу наиболее распространенных типов регистров:

- 1. параллельные регистры;

- 2. последовательные регистры (сдвиговые регистры);

- 3. Универсальные регистры;

- 2. Изучить <u>принципиальную схему лабораторного стенда LESO2</u> и определить какая часть исследуемой схемы реализована аппаратно, а какая будет реализована с помощью среды автоматизированного проектирования Quartus II.

- 3. Разработать четыре принципиальные схемы исследования параллельных и последовательных регистров к пунктам 1 ... 4

#### Задание к работе

1.Исследовать параллельный регистр-защёлку

Соединить четыре <u>D триггера</u>, работающих по потенциалу (триггер защёлка, в Quartus он называется "latch"), параллельно. Входы триггеров подключить к переключателям S5 ... S8. Выходы триггеров подключить к светодиодам LED5 ... LED8. Входы синхронизации триггеров соединить параллельно и подключить к переключателю S1. Сконфигурировать ПЛИС в соответствии с разработанной схемой.

Подавая на входы регистра комбинации логических уровней, приведенных в таблице 1, с помощью ключей S5 ... S8 и наблюдая за состояниями светодиодных индикаторов LED5 ... LED8, заполните её пустые колонки. Обратите внимание! Строки, где на входе С последовательно присутствует логическая единица формируют один импульс. Не нужно каждый раз щелкать переключателем.

Таблица 1. Сигналы на входах и выходах регистра-защёлки

| D0 | <b>D1</b> | D2 | D3 | C | Q0(t) | Q1(t) | Q2(t) | Q3(t) |

|----|-----------|----|----|---|-------|-------|-------|-------|

| 0  | 1         | 0  | 1  | 0 |       |       |       |       |

| 0  | 1         | 0  | 1  | 1 |       |       |       |       |

| 0  | 1         | 0  | 1  | 0 |       |       |       |       |

| 0  | 1         | 1  | 1  | 0 |       |       |       |       |

| 0 | 1 | 1 | 1 | 1 |  |  |

|---|---|---|---|---|--|--|

| 0 | 1 | 1 | 1 | 0 |  |  |

| 1 | 1 | 0 | 1 | 0 |  |  |

| 1 | 1 | 1 | 1 | 1 |  |  |

| 1 | 0 | 1 | 1 | 1 |  |  |

| 1 | 0 | 0 | 0 | 1 |  |  |

| 1 | 0 | 0 | 0 | 0 |  |  |

| 0 | 0 | 0 | 1 | 0 |  |  |

# 2.Исследовать параллельный регистр

Заменить в схеме регистра триггеры, работающие по потенциалу на <u>D триггеры</u>, работающие по фронту. В системе проектирования Quartus II это элемент памяти dff. Сконфигурировать ПЛИС в лабораторном стенде в соответствии с новой схемой.

Подавая на входы регистра комбинации логических уровней, приведенных в таблице 1, с помощью ключей S5 ... S8 и наблюдая за состояниями светодиодных индикаторов LED5 ... LED8, заполните таблицу 2. Обратите внимание на отличие в таблицах!

# 3. Исследовать работу последовательно-параллельного регистра

Увеличить количество триггеров в схеме регистра до восьми. Выходы триггеров подключить к светодиодам LED5 ... LED8. Соединить триггеры в схеме регистра последовательно. При этом на входах регистра останется только два переключателя — S5 на входе D0 и переключатель S1 на входе синхронизации C. Сконфигурировать ПЛИС в лабораторном стенде в соответствии с новой схемой.

При помощи переключателя S5 ввести в регистр число, соответствующее номеру бригады + 224 (например для бригады №1 код будет равен 11100001<sub>2</sub>). Каждый бит должен сопровождаться импульсом на входе синхронизации С. Для этого при помощи переключателя S1 нужно последовательно подать логическую 1, а затем логический 0. Следующий бит на входе D0 следует устанавливать только после завершения формирования импулься синхронизации CLK.

После каждого импульса записать данные на выходе последовательного регистра в таблицу 3. Обратите внимание по какому фронту происходит изменение выходного состояния регистра. Пример заполнения таблицы 3:

| D0 | C     | Q0(t) | Q1(t) | Q2(t) | Q3(t) | Q4(t) | <b>Q5(t)</b> | <b>Q6(t)</b> | Q7(t) |

|----|-------|-------|-------|-------|-------|-------|--------------|--------------|-------|

| 0  | _ - _ | 0     | 0     | 0     | 0     | 0     | 0            | 0            | 0     |

| 0 | _ - _ | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|-------|---|---|---|---|---|---|---|---|

| 1 | _ - _ | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | _ - _ | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | _ - _ | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | _ - _ | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1 | _ - _ | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | _ - _ | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

**Повторить выполненные действия с реальной микросхемой 1533ИР8**. В среде автоматизированного проектирования Quartus II этой микросхеме соответствует примитив 74164.

# 4. Исследовать работу параллельно-последовательного регистра

Исследование параллельно-последовательного регистра начнем сразу с реальной микросхемы, подобной 555ИР1. Создайте на этой микросхеме 8-разрядный регистр. В среде автоматизированного проектирования Quartus II микросхеме 555ИР1 соответствует примитив 7495. Вместо двух 4-разрядных микросхем 555ИР1 можно применить 8-разрядный регистр 74198 или 74166.

Сконфигурируйте ПЛИС в соответствии с созданной вами схемой. Для индикации переданного кода следует использовать схему, исследованную нами в предыдущем пункте (последовательно-параллельный регистр с подключенными к его выходам восемью светодиодами)

Обратите внимание, что в исследуемой схеме появился дополнительный управляющий вход МОDE. Этот вход переключает регистр либо в режим параллельной записи (МОDE=1), либо в режим последовательного сдвига. Не забывайте, что при параллельной записи в регистр передаваемого вами кода тоже требуется импульс записи!

## Содержание отчета

- 1. Цель работы;

- 2. Схема исследования регистра-защелки;

- 3. Таблица логических уровней на входах и выходах регистра-защелки (по результатам эксперимента);

- 4. Временные диаграммы работы параллельного регистра-защелки (Обратите внимание на форму синхроимпульсов);

- 5. Схема исследования параллельного регистра;

- 6. Таблица логических уровней на входах и выходах параллельного регистра на D—триггерах (по результатам эксперимента);

- 7. Временные диаграммы работы параллельного регистра на D—триггерах (Обратите внимание на форму синхроимпульсов);

- 8. Схема исследования последовательно-параллельного регистра;

- 9. Таблица логических уровней на входах и выходах последовательно-параллельного регистра;

- 10.Временные диаграммы работы последовательно-параллельного регистра (Обратите внимание на положение фронтов синхроимпульсов);

- 11.Схема исследования параллельно-последовательного регистра;

- 12. Таблица логических уровней на входах и выходах параллельно-последовательного регистра;

- 13. Временные диаграммы работы параллельно-последовательного регистра (по результатам эксперимента);

- 14. Выводы по каждому заданию.

# Контрольные вопросы

- 1. Назначение регистров?

- 2. По каким признакам классифицируются регистры?

- 3. Чем определяется разрядность регистров?

- 4. Назначение параллельного регистра?

- 5. Объяснить принцип работы параллельного регистра.

- 6. Объяснить принцип работы последовательного регистра.

- 7. Объяснить принцип работы последовательно-параллельного регистра.

- 8. Зачем применяются последовательно-параллельные регистры?

- 9. Объяснить принцип работы параллельно-последовательного регистра?

- 10.Зачем применяются параллельно-последовательные регистры?

- 11. Внутреннее устройство универсальных последовательных регистров?

# Лабораторная работа №4

Исследование функциональных схем шифраторов и дешифраторов

**Цель работы:** Целью работы является изучение принципов действия комбинационных устройств: дешифратора, шифратора, преобразователя кода для семисегментного индикатора, мультиплексора, сумматора.

# Подготовка к лабораторной работе

По <u>конспекту</u> лекций изучить работу наиболее распространенных <u>комбинационных схем</u>:

- 1. дешифратора (декодера);

- 2. шифратора (кодера);

- 3. семисегментного дешифратора;

- 4. мультиплексора;

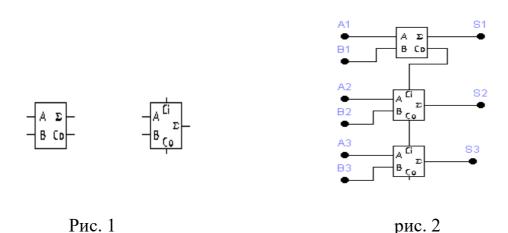

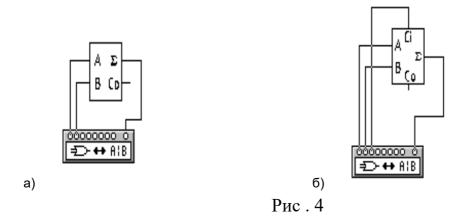

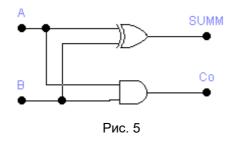

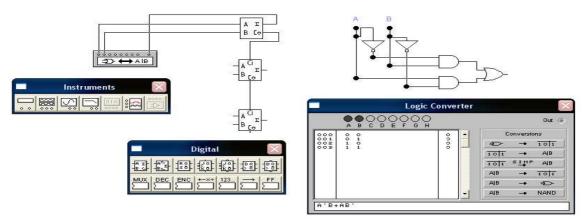

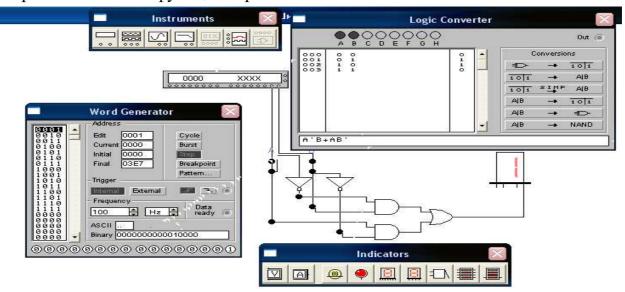

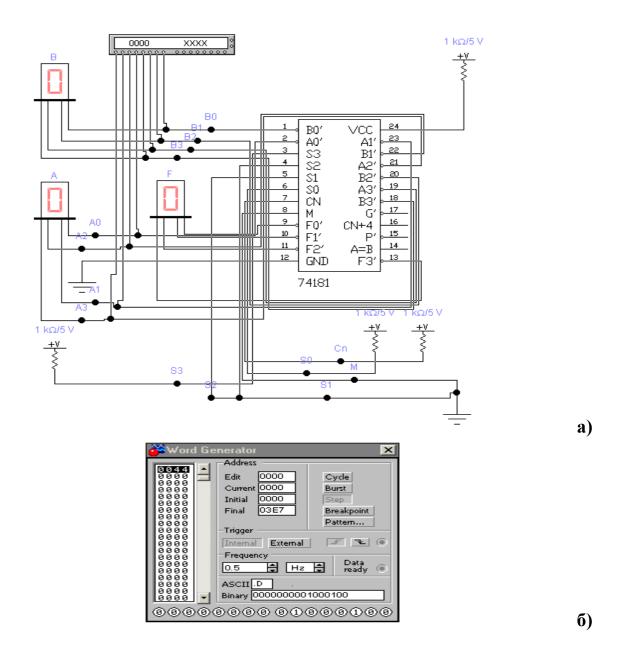

### 5. полного двоичного сумматора.

Изучить <u>принципиальную схему лабораторного стенда LESO2</u> и определить какая часть исследуемой схемы реализована аппаратно, а какая будет реализована с помощью среды автоматизированного проектирования Quartus II.

### Задание к работе

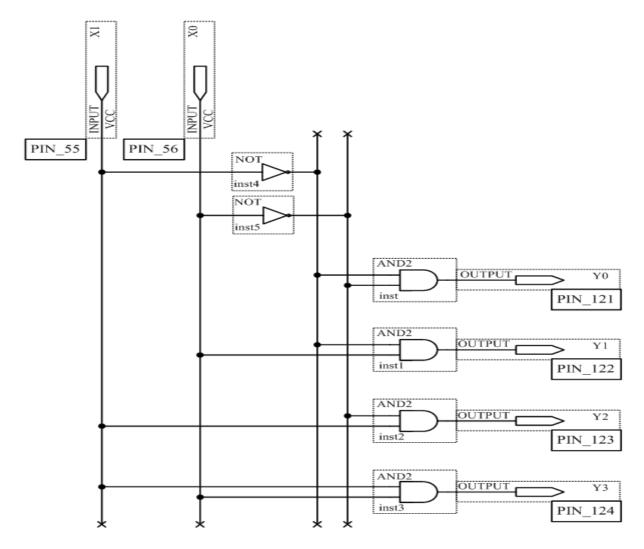

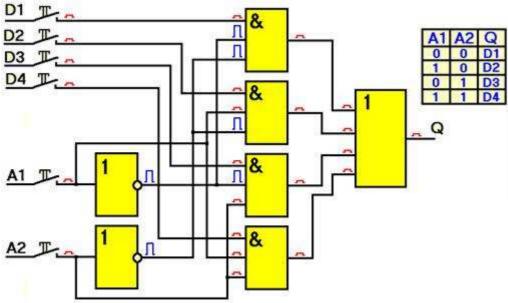

#### 1. Исследовать принцип работы дешифратора 2х4

Сконфигурировать ПЛИС в соответствии с рисунком 1. Подключить к входам X0 и X1 переключатели S7 и S8, а к выходам Y0, Y1, Y2, Y3 светодиодные индикаторы LED5, LED6, LED7, LED8. Для этого подключить входы и выходы дешифратора к соответствующим выводам ПЛИС.

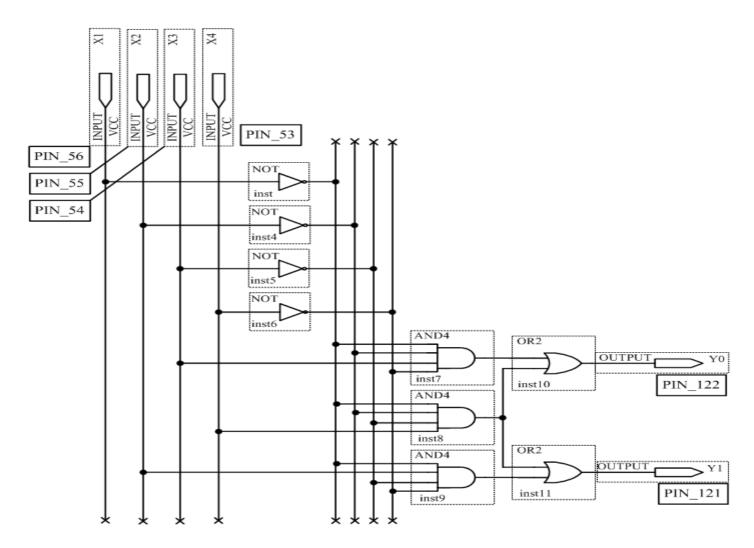

Рисунок 1. Схема дешифратора в графическом редакторе САПР Quartus II

Подавая все возможные комбинации логических уровней на входы X0, X1 с помощью ключей S7, S8 и наблюдая за состояниями светодиодных индикаторов LED5, LED6, LED7, LED8, заполните таблицу истинности дешифратора.

Таблица 1. Таблица истинности дешифратора

| <b>x1</b> | <b>x2</b> | y0 | y1 | y2 | y3 |

|-----------|-----------|----|----|----|----|

| 0         | 0         |    |    |    |    |

| 0         | 1         |    |    |    |    |

| 1         | 0         |    |    |    |    |

| 1         | 1         |    |    |    |    |

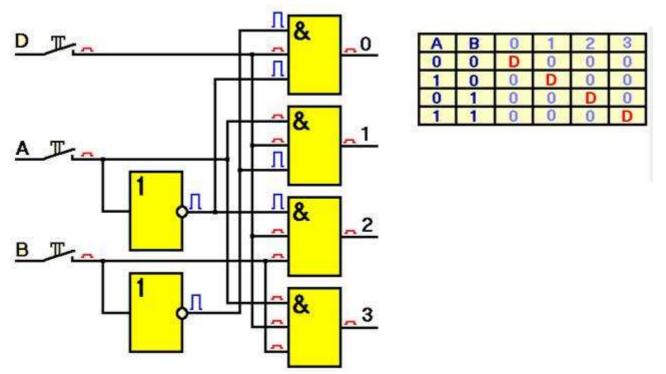

# 2. Исследовать принцип работы шифратора 4х2

Сконфигурировать ПЛИС в соответствии с рисунком 2.

Рисунок 2. Принципиальная схема шифратора 4x2 в графическом редакторе САПР Quartus II

Подключить к входам X1, X2, X3, X4 переключатели S8, S7, S6, S5, а к выходам Y0, Y1 светодиодные индикаторы LED8, LED7. Для этого подключить входы и

выходы дешифратора к соответствующим ножкам ПЛИС. Подавая все возможные комбинации логических уровней на входы X1, X2, X3, X4 с помощью ключей S8, S7, S6, S5 и наблюдая за состояниями светодиодных индикаторов LED7, LED8, заполните таблицу истинности шифратора.

Таблица 2. Таблица истинности шифратора

| x1 | <b>x2</b> | <b>x3</b> | <b>x4</b> | y1 | y0 |

|----|-----------|-----------|-----------|----|----|

| 1  | 0         | 0         | 0         |    |    |

| 0  | 1         | 0         | 0         |    |    |

| 0  | 0         | 1         | 0         |    |    |

| 0  | 0         | 0         | 1         |    |    |

# 3. Исследовать работу семисегментного дешифратора.

Составить таблицу истинности семисегментного дешифратора (таблица 3). Для этого в графическом редакторе собрать схему, изображенную на рисунке 3.

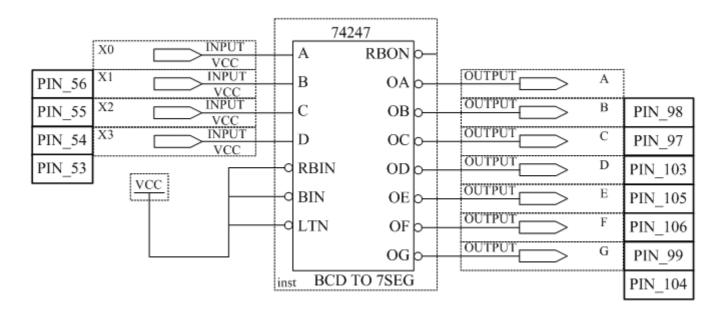

Рисунок 3. Схема семисегментного дешифратора

Подавая с помощью ключей S8, S7, S6, S5 различные кодовые комбинации на входы X0, X1, X2, X3 определить цифры, высвечиваемые на индикаторе. По результатам эксперимента заполнить левую колонку таблицы 3.

Таблица 3. Таблица истинности семисегментного дешифратора

| $\mathbf{x}$ 3 | x2 x1 | $\mathbf{x0}$ | a l | c | d | e | f | g | Показание индикатора |  |

|----------------|-------|---------------|-----|---|---|---|---|---|----------------------|--|